CONNECTING

SYSTEMS TO

**DISPLAYS:**

WHAT WE GOT

CLICK HERE TO RENEW

Page 46

HERE IS FAILURE TO

COMMUNICATE

# Ultimate Precision. Low Power. Small Size.

### **Amplifiers Use TI's New 36V Bipolar SiGe Process**

| Device | Input   | V <sub>N</sub> | V <sub>os</sub> | GBW   | lα    | Vs   | Package |

|--------|---------|----------------|-----------------|-------|-------|------|---------|

| OPA211 | Bipolar | 1nV/√Hz        | 100μV           | 80MHz | 3.5mA | ±18V | MSOP-8  |

| OPA827 | JFET    | 4.5nV/√Hz      | 250µV           | 18MHz | 4.2mA | ±18V | MSOP-8  |

The new OPA211 and OPA827 precision amplifiers from Texas Instruments offer lower power, smaller package size and lower noise, enabling breakthrough performance in test and measurement, instrumentation, imaging, medical, audio and industrial process control applications. The amplifiers were developed using the industry's first complementary bipolar 36V SiGe process, BiCom3HV.

# RECEIVE A FREE PRODUCT CATALOG!

Now Featuring: More Wireless Components Than Ever!

Visit www.digikey.com/catalog

Quality Electronic Components, Superior Service

www.digikey.com • 1.800.344.4539

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

# **Ancient Methods of Protection Will Only Take You So Far.**

When it comes to thwarting 21st century evildoers, nobody has more industry-proven secure IC solutions than Atmel®.

With a broad portfolio of biometric sensors, embedded security chips, RF identification chips, secure microcontrollers and secure memories for smart cards, and RFID/card readers, Atmel has the expertise and flexibility to provide customer-driven solutions for security in an unsecured world.

And, when it comes to measuring why we're good, don't just take our word for it. Our secure microcontroller product portfolio meets the stringent needs of the security market with some of the highest security certifications in the industry, including Common Criteria EAL4+/EAL5+, FIPS-140-2 Level 3 and 4, ZKA, Visa® International and MasterCard CAST approvals.

So, when your next project calls for security, think Atmel. We're Everywhere You Are®... securely.

Secure Memory and Microcontrollers for Smart Cards

Smart Card Reader ICs

Biometrics

Trusted Platform Module IC

**Embedded Security**

RF Identification

Check out Atmel's security solutions today at www.atmel.com/ad/securitysolutions

# YEAH, IT'S THAT FAST. IT'S THAT SIMPLE.

#### Some companies are just known for their consistent quality.

From quote to delivery, we serve up the world's best online PCB ordering. Consistent, quality proto-boards, every time.

www.sunstone.com

- 2-6 layer, quickturn proto-boards

- Complete customer service, 24/7, 365 days a year

- Over 30 years of manufacturing experience

- The ultimate in easy online PCB ordering

"Sunstone has done a great job with all of our orders. We rely on your easy online ordering system, quality boards, and fast lead times."

- Sunstone customer feedback

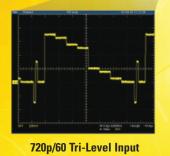

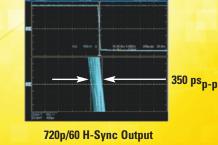

# **Ultra Low-Jitter Sync Separator for SD/HD Video**

**New LMH1981 Features 50% Sync Slicing for Precise Output Timing**

eparator

#### Analog Video to Serial Digital Interface (SDI) Converter Typical Diagram SDI Video Out **Analog Composite Video In** ADC14155 LMH0030 Serializer HD/SD **SDI Cable Driver** Sync Reference Info Clock MH1981 FPGA/ SD/HD PLL

Clock Gen

LMH1981 in TSSOP-14 packaging Shown at actual size 4.40 x 5.00 x 0.90 mm

#### LMH1981 Features

- 50% sync slicing

- Low-jitter horizontal sync outputs

- Supports NTSC, PAL, SECAM, 480i, 480p, 576i, 576p, 720p, 1080i, and 1080p

- $\bullet$  Accepts video sync signals from 140 mV  $_{\text{P-P}}$  to 1.2  $V_{\text{P-P}}$

- No external programming with μC required

- Horizontal sync output propagation delay <50 ns

- 3.3V or 5V single supply operation

#### LMH1981 Outputs

- Horizontal sync

- Vertical sync

**Jitter**

Cleansing

- Odd/Even field

- Burst/back porch clamp

- Composite sync

- Video format (horizontal lines/field)

Ideal for use in sync separation, A/V clock generation, video genlock, back porch clamp generator, video format detection circuit, and analog-to-SDI converter applications

For FREE samples, datasheets, online design tools, and more information on the LMH1981, contact us today at amplifiers.national.com

Or call 1-800-272-9959

# **EDN** contents

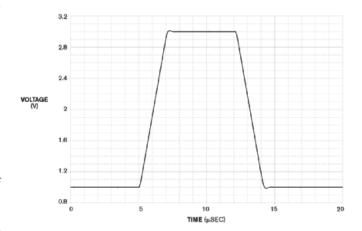

TIME (µSEC)

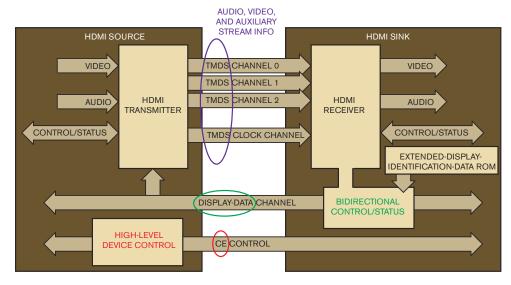

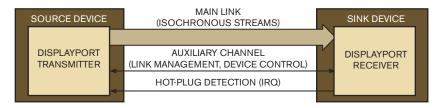

#### **CONNECTING SYSTEMS** TO DISPLAYS:

#### What we got here is failure to communicate

Continuous technological evolution is the inevitable consequence of vendors' desires to sustain revenue and profit at healthy levels. When that product progression results in regressive experiences for end users, however, its sustainability is uncertain.

> by Brian Dipert, Senior Technical Editor

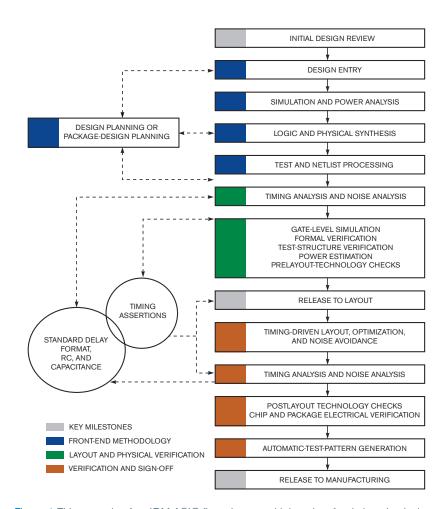

#### Timing is everything in SOC design

Despite good tools, successful timing closure is still a matter of methodology and attention. by Ron Wilson, Executive Editor

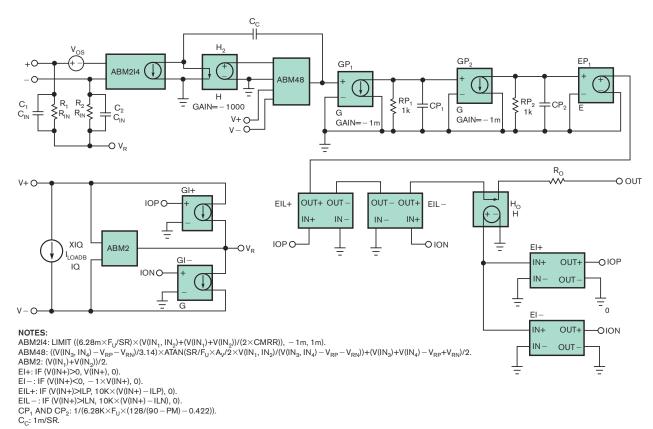

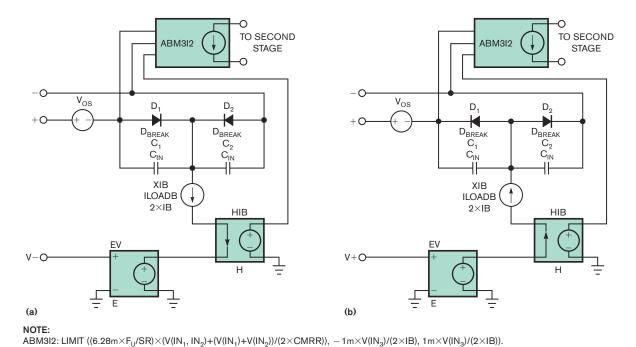

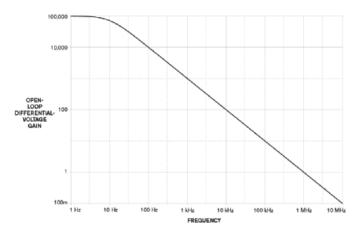

#### User-friendly model simplifies Spice op-amp simulation

A new macromodel based on data-sheet parameters allows easy model creation for new amplifiers. by Ray Kendall, Intuitive Research and Technology Corp

# DESIGNIDEAS

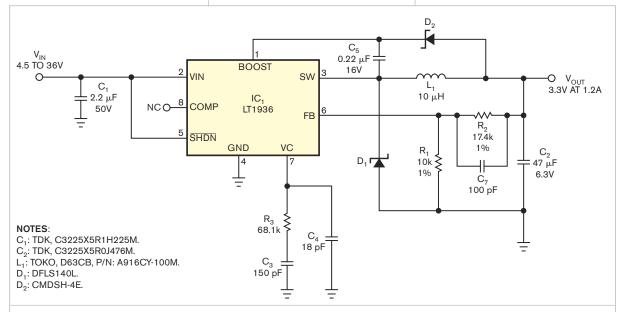

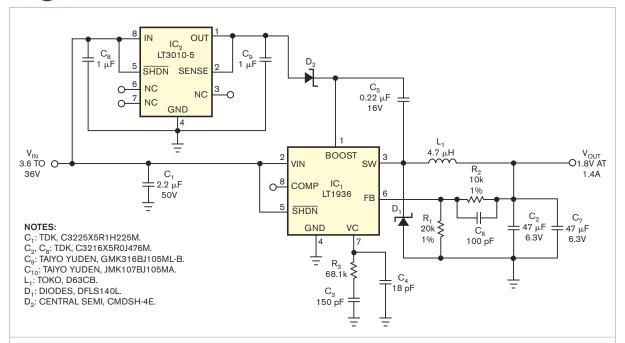

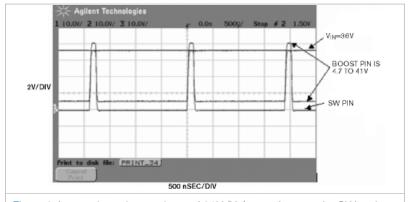

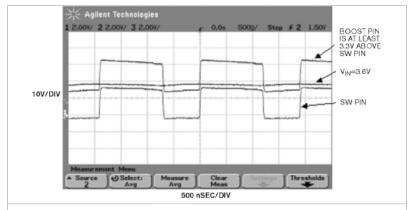

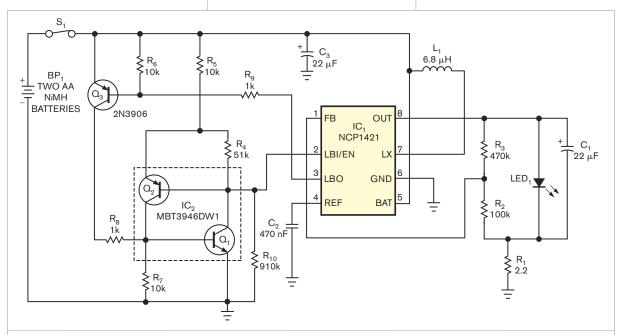

- 71 Extend low-output-voltage switching regulator's input range

- 74 Automatic latch-off circuit saves batteries

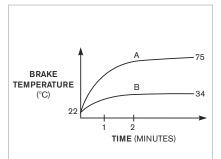

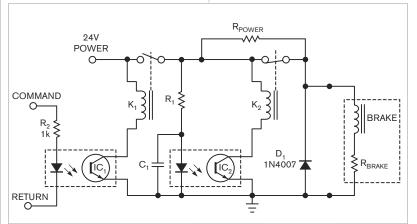

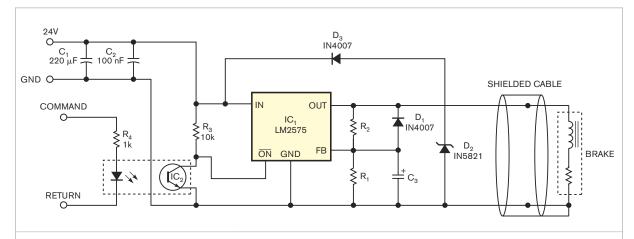

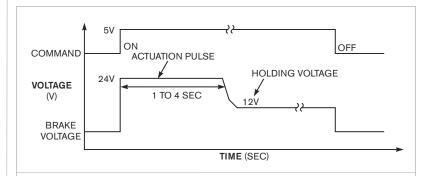

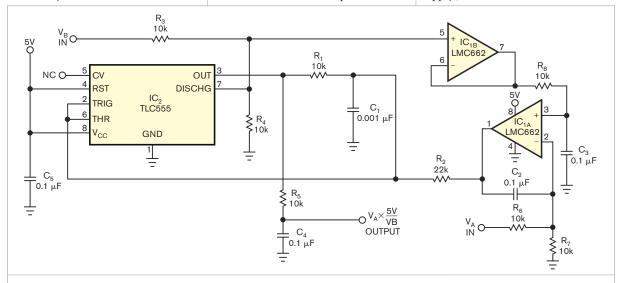

- 76 Switching regulator reduces motor brake's power consumption

- 78 Analog divider uses few components

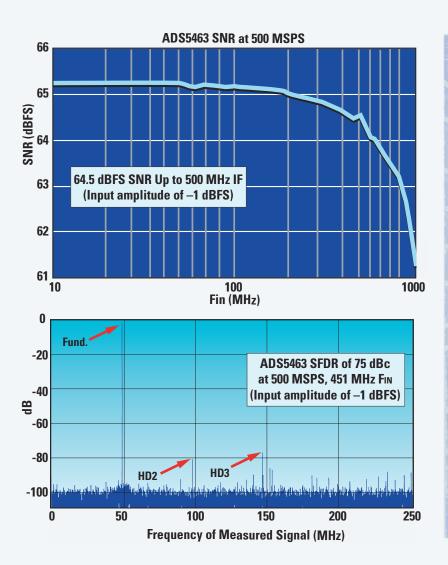

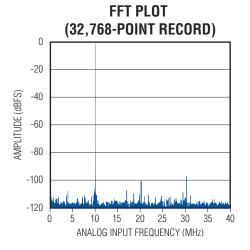

# **12-Bit, 500 MSPS ADC**

The 12-bit, 500 MSPS **ADS5463** from Texas Instruments delivers best-in-class performance with greater than 75 dBc SFDR and 64.5 dBFS SNR for input frequencies through 450MHz. This new ADC benefits the most demanding amplifier linearization, communications, radar, imaging, test and measurement applications – all in a 14mm x 14mm 80-pin TQFP package. The ADS5463 is part of a pin-compatible family of products that include TI's 13-bit 250/210MSPS ADS5444 and ADS5440 ADCs.

www.ti.com/ads5463 · 800.477.8924, ext. 13476

#### **▶** Applications

- Power amplifier linearization

- Multi-carrier receivers

- Software defined radio

- Radar and advanced imaging

- -Test and measurement

#### **▶** Features

- 12-bit resolution, 10.5 ENOB

- 2 GHz input bandwidth

- Space saving package size:80-pin TQFP (14mm x 14mm)

- Differential input: 2.2 Vpp

- LVDS outputs with simplified data capture

- Total power dissipation: 2.25W

- Ind. temp: ADS5463 -40° C to +85° C

- Mil. temp: ADS5463-EP, QMLV

-55° C to +125° C

- Pin-compatible with 13-bit,210 MSPS ADS5440 and13-bit, 250 MSPS ADS5444

- Recommended amplifiers: THS9000, THS9001, THS4304, THS4509, THS4511

- In production now: Priced at \$125 in 1k units (Industrial temp. only)

For Evaluation Modules, Samples and Technical Information

Technology for Innovators™

### contents 1.04.07

- 17 High-speed modular logic analyzers capture as many as 512M samples

- 18 Processor lowers cost of Gigabit Ethernet

- 18 EPIC computer expands communications options

- 20 ESL market adds an enterprise player

- 22 Dummy-fill-synthesis tool has smarts

- 22 WiQuest adds video support to Wireless USB

- 24 Global Designer: Point-and-see picture transfer requires no setup, employs IrDA; Powering SOCs with integrated approaches

### DEPARTMENTS & COLUMNS

- 12 **EDN.comment:** Foggy crystal ball yields 2007 wishes

- 26 Signal Integrity: Two-way street

- **Tales from the Cube:** Testing our reliance on testing

- 30 **Prying Eyes:** Under the hood of hybrid vehicles

- 84 **Scope:** The 2007 International Solid-State Circuits conference, early desktop computing, and the Consumer Electronics Show

### PRODUCT ROUNDUP

- 80 **Discrete Semiconductors:** Power MOSFETs, bipolar-junction transistors, high-current-density miniature packaging, and more

- **81 Embedded Systems:** Blade servers, PCI CPU cards with wireless support, and input modules

EDN® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Read Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Ciniel Executive Officer; Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2007 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year; Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40865520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6J3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc. used under license. A Reed Business Information Publication/Volume 52, Number 1 (Printed in USA).

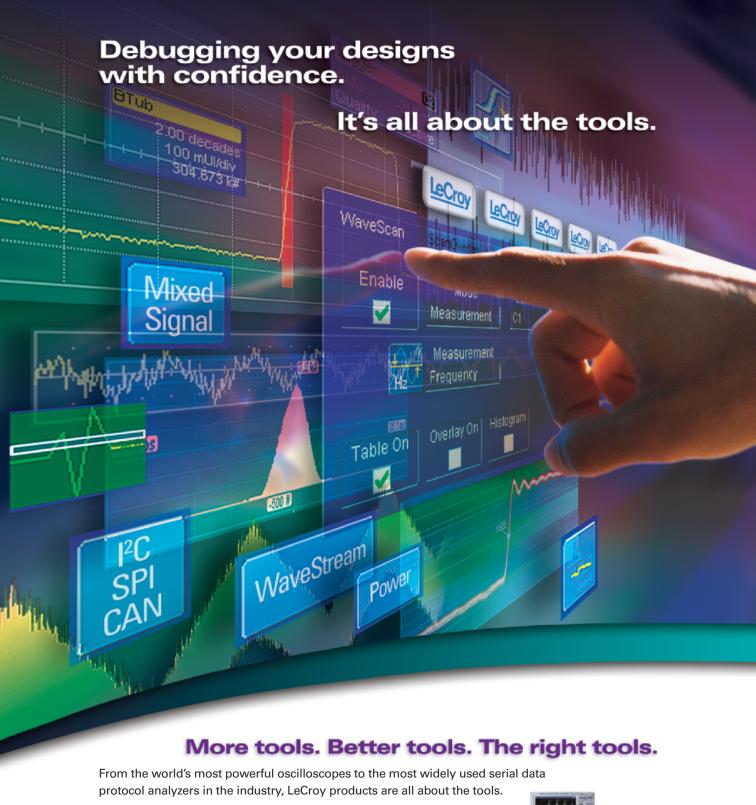

Now the LeCroy toolbox is more powerful than ever in oscilloscopes you didn't know you could afford. From 200 MHz to 2 GHz, LeCroy scopes offer more analysis and debug tools than anyone else at prices from \$3,000. So what are you waiting for? Find the right tool for your design debug job at LeCroy. We're all about the tools.

# online contents

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Low-cost, high-I/O-count FPGAs target display market

In an attempt to nab sockets in the market for low-cost, high-volume video displays, Xilinx has released an I/O-heavy version of its 90-nm Spartan-3 FPGAs.

www.edn.com/article/CA6397968

#### Benefits of adding an active clamp to a synchronous flyback power supply

Active-clamp forward converters have been an increasingly popular choice in higher power applications. Yet few power-supply designers are aware that they can also employ an active clamp in flyback converters. www.edn.com/article/CA6399933

#### Risk reduction in a verification upgrade

Chip-design managers cannot afford to wait for conclusive evidence before looking at adopting new verification methodologies. Therefore, it is important to have in place a good policy for minimizing the risks associated with adoption and assessing the impact of each change.

www.edn.com/article/CA6396963

#### Hard-disk-drive seminar discusses road map for PMR

Perpendicular magnetic recording may help the disk-drive industry maintain its costper-bit advantage over flash memory but not without significant advances throughout the read channel.

www.edn.com/article/CA6399873

#### Practical book helps developers apply USB-interfaced mass-storage devices

In technical writing, clarity is the name of

www.edn.com/article/CA6397836

#### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

#### Low-cost kits:

#### the new FPGA-designer trend

www.edn.com/article/CA6391429

#### Infineon shows full chip employing finFET circuits

www.edn.com/article/CA6396816

#### Creating the power subsystem in modern design

www.edn.com/article/CA6395488

#### Active-filter circuit and oscilloscope inspect a Class D amplifier's output www.edn.com/article/CA6395489

#### Get power from a telephone line without disturbing it

www.edn.com/article/CA6395493

#### Battling bugs:

#### embedded debugging tactics

www.edn.com/article/CA6395499

#### Hit the ground running: Detective work revives vintage vector voltmeter

www.edn.com/article/CA6395512

#### Voices: Microsoft's Amir Maiidimehr: a "window" to the world of digital media

www.edn.com/article/CA6391444

#### Nonfailing light-bulb-string story causes readers to think

www.edn.com/article/CA46589

### Simple tester checks Christmas-tree

www.edn.com/article/CA46423

#### INNOVATION AWARDS

#### **TICKETS ON SALE NOW!**

Tickets for EDN's annual Innovation Awards banquet are now on sale. The event will take place April 2, 2007, in San Jose, CA. Visit www.edn.com/innovation for more details and to order your tickets today. Order before February 2 and receive the special early-bird ticket price.

#### HOT 100 PRODUCTS of 2006

As 2007 gets underway and we prepare for a whole new batch of hot products in the year to come, take a look back at the ones to beat from 2006! Our list distills the most innovative and significant products of the year, including process technologies, power sources, storage devices, processors, intellectual-property cores, communication controllers, test instruments, embedded boards. EDA tools, and more.

www.edn.com/2006hot100

#### FAST-FORWARD YOUR PROJECT WITH WINDOWS® EMBEDDED.

Change happens. Don't let it slow you down. Get to market faster with end-to-end development toolkits, building blocks to create tailored solutions, and the support of a highly qualified partner community. See how Magellan cut six months from development of its devices at **microsoft.com/embedded**

#### BY MAURY WRIGHT, EDITOR IN CHIEF

# Foggy crystal ball yields 2007 wishes

ell, 2007 has arrived, along with the New Year's resolutions and the ever-present pundit technology predictions. Unfortunately, my crystal ball is a bit foggy when it comes to such things as wireless LANs, video over Internet Protocol, UWB (ultrawideband), and home-video networks. So, rather than offer a set of predictions for tech in 2007, I'll offer a short

list of wishes. Given the track record of the principals, I'm not confident that I'll see my wishes fulfilled. But I'm sure the tech industry would be better off if they do come true.

For starters, I'm hoping the IEEE 802.11n players finally come to an understanding. Their bickering hasn't stopped consumers from buying up Wi-Fi gear. Wi-Fi is now a standard feature in notebooks and is coming soon to handsets. But we've yet to have a chance to really figure out whether 802.11n might serve up whole-house video. I'm also just tired of the posturing and words such as "draft-n-compliant." And although I've been an Airgo supporter, the company even further crossed the line by declaring "draft-2.0" compliance with its recent chip announcement that coincided with the announcement that Qualcomm would acquire Airgo.

I'm also wishing for the streets in my neighborhood to be excavated once again. I hate the inconvenience but recognize that fiber must reach North American homes. AT&T has boasted that its U-Verse service is 100% video over IP. But AT&T isn't pushing fiber all the way to the home, and, even with VDSL2, the service provider will strug-

# I hope the UWB crowd either finally delivers products in 2007 or just disappears.

gle to offer compelling HDTV services. Verizon is pushing fiber to homes, but mainly only in new developments or in areas where the company can string the fiber overhead. Meanwhile, Korea, Japan, and China are all working on massive fiber deployments. We need fiber for symmetrical data services and the best in video services, including true on-demand service. The last mile is still gating what can happen behind it in the core networks and in front of it in homes.

I hope the UWB crowd either finally delivers products in 2007 or just disappears. The Wireless USB supporters that base the cable-replacement technology on UWB appear close. But most of the chip vendors had pledged that end products would ship for the 2006 holiday season. No luck there. I'm also unsure about how fast consumers will adopt a nice-to-have technology such as Wireless

USB. The success may depend on how well it handles video, even over short distances. And Tzero Technologies is still claiming that its flavor of UWB can serve up whole-house video. If it does, I'll be first in line.

Perhaps my most fervent hope is that some industry players will again move toward the goal of building great products rather than chasing royalty streams. Sony has long been my favorite target in this regard. I was once one of Sony's biggest fans. At one time, my living room was all-Sony. Today a single, and admittedly dated, Sony DVD player is still present. Of late, Sony proves time and again that it cares more about getting IP adopted into standards such as next-generation DVD players than it does about building great products that consumers want to buy. The company isn't happy with just making money selling consumer products; it wants a slice of competitors' revenue as well, such as it has seen from the audio CD. It's increasingly clear that the strategy hasn't served Sony well; the company has lost status as a premium brand.

Unfortunately, the patent-troll philosophy isn't limited to Sony. Qualcomm has been guilty to some extent. Patriot Scientific comes to mind in the microprocessor area. It appears that former Microsoft executive and industry luminary Nathan Myhrvold plans to build a business around all types of IP with his Intellectual Ventures.

I'm not sure that we wouldn't be much better off with more open cross-licensing. One of the best interviews I did in 2006 was with Wally Rhines, Mentor's chief executive officer, in preparation for our 50th-anniversary issue last September. Rhines believes that massive cross-licensing in the early days of the semiconductor industry made for the explosive growth that we witnessed over several decades. We aren't seeing that growth these days.EDN

Contact me at mgwright@edn.com.

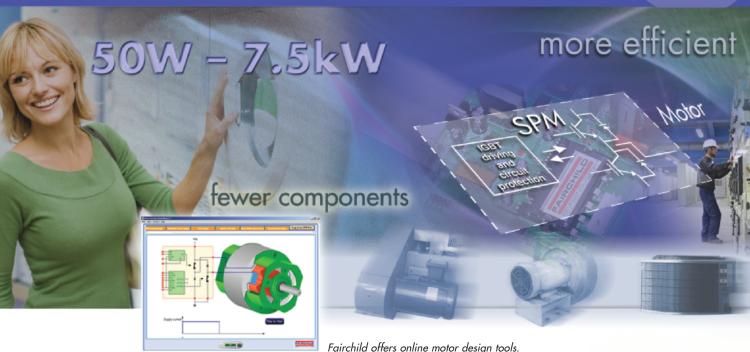

# Energy-saving inverter designs: 50% less cost, size and time.

#### Integrated power modules simplify your designs

Smart Power Modules (SPM<sup>TM</sup>) are just what you need to dramatically improve the performance/cost ratio of variable speed designs. Available for motor ratings from 50W to 7.5kW, every SPM includes:

- An integrated drive and protection solution built with our leading power components

- Fairchild's combined power and motion design expertise

- Best-in-class packaging technology that reduces board space while providing excellent thermal performance

| SPM<br>Series | Motor<br>Ratings | Description                          |

|---------------|------------------|--------------------------------------|

| Motion-SPM    | 50W to 7.5kW     | 3-phase IGBT or MOSFET inverter      |

| SRM-SPM       | 2kW              | Single-phase asymmetric bridge       |

| PFC-SPM       | 1kW to 3kW       | Partial switching converter module   |

| FT C-SFIM     | 3kW to 6kW       | Power Factor Correction (PFC) module |

Our SPM series includes solutions for consumer and industrial inverter designs, as well as options for switched reluctance and PFC.

If you prefer to build your own drive with discrete components, all the building blocks inside our SPM, including IGBTs, HVICs and MOSFETs are also available for your motion power path.

If energy and cost savings are your problem, Fairchild has your solution.

For more motor design information, including online design tools and application notes, visit www.fairchildsemi.com/motor.

problem solved

www.fairchildsemi.com

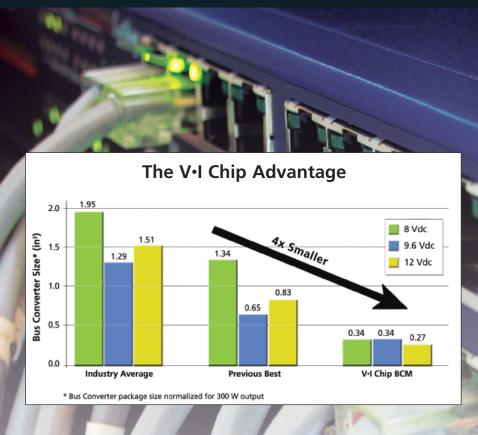

# Twice the Power

## Half the Size

#### 48 V Bus Converters Increase Port Density and Processing Throughput

| BCM<br>Model No. | Vout<br>(V) | Max Power<br>(W) | Peak Efficiency<br>(%) |

|------------------|-------------|------------------|------------------------|

| B048F015T14      | 1.5         | 140 W            | 91.5                   |

| B048F030T21      | 3.0         | 210 W            | 95.0                   |

| B048F040T20      | 4.0         | 200 W            | 94.8                   |

| B048F060T24      | 6.0         | 240 W            | 95.6                   |

| B048F080T24      | 8.0         | 240 W            | 96.0                   |

| B048F096T24      | 9.6         | 240 W            | 96.2                   |

| B048F120T30      | 12.0        | 300 W            | 95.1                   |

| B048F160T24      | 16.0        | 240 W            | 96.0                   |

| B048F240T30      | 24.0        | 300 W            | 95.7                   |

| B048F320T30      | 32.0        | 300 W            | 96.5                   |

| B048F480T30      | 48.0        | 300 W            | 96.7                   |

#### 48 V Bus Converter Module

- 300 W Converter in 1/16 Brick Area

- 1.1 in<sup>2</sup> Footprint, 1/4 in Low Profile

- Runs Cool

- 97% Efficiency

The new 48 V Bus Converter Modules (BCMs) offer 4x the power density, freeing board space for data processing and I/O functions, and increasing port density and triple play (voice/video/internet) traffic capacity.

Contact us now for comprehensive design-in support, evaluation boards and technical documentation via www.vicorpower.com/bcmedn or call 800-735-6200.

All parts in mass production and available from stock NOW!

### EDN

#### PUBLISHER. EDN WORLDWIDE

John Schirmer 1-408-345-4402: fax: 1-408-345-4400: jschirmer@reedbusiness.com

#### **EDITOR IN CHIEF**

Maury Wright, 1-858-748-6785; mgwright@edn.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Kasev Clark 1-781-734-8436; fax: 1-781-290-3436; kase@reedbusiness.com

#### **EXECUTIVE EDITOR. ONLINE**

#### Matthew Miller

1-781-734-8446: fax: 1-781-290-3446: mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@reedbusiness.com

#### EDA, MEMORY, PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor 1-408-345-4424;

michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs, TOOLS

Robert Crayotta, Technical Editor 1-661-296-5096; fax: 1-781-734-8070; rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA. **PCs AND PERIPHERALS**

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-781-734-8038; bdipert@edn.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### **DESIGN IDEAS EDITOR**

**Brad Thompson** edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439: f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-347-9605; mbutler@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager 1-781-734-8445; fax: 1-781-290-3445 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-781-290-3442 Melissa Annand, Newsletter/Editorial Coordinator Contact for contributed technical articles 1-781-734-8443; fax: 1-781-290-3443 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-781-290-3325

#### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; aprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

#### **EDN CHINA**

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.ip Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.jp Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### **DENNIS BROPHY**

Director of Business Development. Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV

System Architect Intel

#### RON MANCINI

Engineer

#### **GABRIEL PATULEA**

Design Engineer, Cisco

#### MIHIR RAVEL VP Technology, National Instruments

DAVE ROBERTSON

#### Product Line Director, Analog Devices

SCOTT SMYERS

VP Network and System Architecture Division, Sony TOM SZOLYGA

#### Program Manager, Hewlett-Packard

JIM WILLIAMS

#### Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reed business.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# **USB Data Acquisition**

#### **Low-Cost Data Acquisition** Starting at \$99

- Up to 16 bits, 250 kS/s, 16 channels

- · Highly portable, USB bus-powered

#### **Full-Featured, Multifunction DAQ**

- Up to 16 bits, 1.25 MS/s, 32 channels

- · Isolated options for measurement accuracy and reliability

#### High-Performance, Modular I/O

- Up to 24 bits, 3.2 MS/s, 256 channels

- · Modules for sensor inputs, analog I/O, digital I/O

To find the perfect USB device for your system, visit ni.com/usb.

(800) 327 9894

© 2006 National Instruments. All rights reserved. CompactRIO, National Instruments, NI, ni.com, and NI CompactDAQ are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 7778-301-101

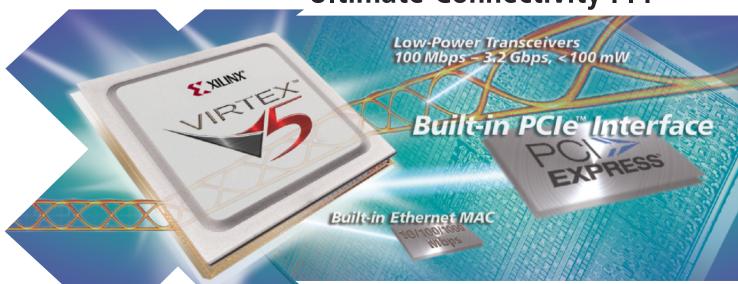

LOW-POWER TRANSCEIVERS

Ultimate Connectivity . . .

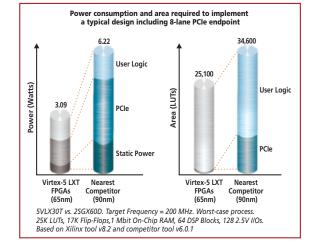

Reduce serial I/O power, cost and complexity with the world's first 65nm FPGAs.

With a unique combination of up to 24 low-power transceivers, and built-in PCle<sup>™</sup> and Ethernet MAC blocks, Virtex-5 LXT FPGAs get your system running fast. Whether you are an expert or just starting out, only Xilinx delivers this complete solution to simplify high-speed serial design.

#### Lowest-power, most area-efficient serial I/O solution

RocketIO™ GTP transceivers deliver up to 3.2 Gbps connectivity at less than 100 mW to help you beat your power budget. The embedded PCI Express® endpoint block ensures easy implementation and reduced development time. Embedded Ethernet MAC blocks enable a single-chip UNH-verified implementation. And the Xilinx solution is fully supported by development tools, design kits, IP, characterization reports, and more.

Visit our website today, view the Webcast, and order your free eval CD to give your next design the ultimate in connectivity.

The Ultimate System Integration Platform

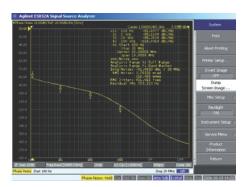

### High-speed modular logic analyzers capture as many as 512M samples

gilent Technologies has expanded its logic-analyzer line with a new modular mainframe; two new modules, including one that provides four times the memory of the deepest memory logic-analyzer modules available from any manufacturer; and new applications for developers who use the PCle (PCI Express) high-speed serial bus and Altera (www.altera. com) FPGAs.

Design teams in the computer, communications, semiconductor, aerospace, defense, automotive, and wireless industries continue to produce ever more complex high-speed-hardware designs. Validation and debugging of these designs necessitate increasingly capable logic-analysis tools. The 16900 product family addresses these reauirements.

The two-slot, modular 16901A mainframe, with prices starting at \$14,000, comes with a 15-in. display and a touchscreen interface that works well in applications in which limited bench space hinders the use of a mouse and keyboard. The mainframe allows connection and crosstriggering of other 16900-series mainframes in applications

The two-slot, modular 16901A logic analyzer sports a 15-in. touchscreen display.

that require more than one logic analyzer.

The 68-channel 16950B logic-analyzer module, with prices starting at \$23,500, offers state-analysis capture to 667 MHz at a maximum data rate of 1066 Mbps with as much as 64M samples of acquisition memory. The module offers the performance necessary to validate such leading-edge interfaces as DDR3 (double-datarate 3) and front-side-bus designs.

The \$65,000, 68-channel 16951B logic-analyzer module offers the same acquisition capabilities as the 16950B but quadruples the maximum memory depth to 256M samples, improving the probability that captured data will contain the flaw that caused a failure.

Moreover, if you use only half of the channels, the memory depth doubles again-to 512M samples.

Two new applications speed the development of PCIe and Altera FPGA-based designs: The FSI-60112 PCIe Gen 1 probe, with prices starting at \$24,700, supports the PCIe standard in one-, two-, and four-lane widths. When you use it with the 16800 portable logic analyzer, the probe offers what the manufacturer calls the market's lowest cost logic-analyzer-based PCIe-test approach. The B4656A FPGA dynamic probe, with prices starting at \$3000, provides visibility into designs based on Altera FPGAs, thus speeding debugging and validation.

#### -by Dan Strassberg ▶Agilent Technologies, www.agilent.com/find/16900.

#### **FEEDBACK LOOP**

"Nothing beats wind power for common sense—so common that, while governor of Texas, George W Bush pushed for funding, support, and commitment to the effort that makes Texas the leader in wind power now. He ought to make the same moves from Washington now."

—Dick Davies in EDN's Feedback Loop at www.edn.com/ article/CA6399098. Add your comments.

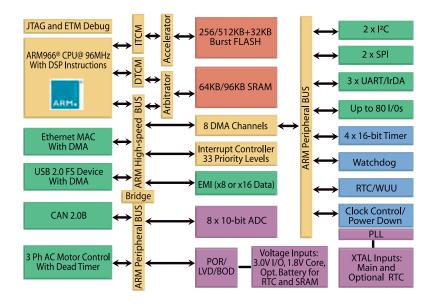

#### PROCESSOR LOWERS COST OF GIGABIT ETHERNET

Freescale's MPC8313E PowerQuicc II Pro processor delivers Gigabit Ethernet with integrated security-encryption blocks for as low as \$15 (10,000). It includes a dual 10-, 100-, 1000-Gbps Ethernet MAC (multiply/accumulate) unit with dual MII (media-independent interface), RGMII (reduced-Gigabit-MII), RTBI (reduced 10-bit interface), RMII (reduced MII), and SGMII (serial-Gigabit MII), and it supports the IEEE 1588 timing protocol. The Power Architecture e300 core operates at clock rates as high as 400 MHz. The device includes an MMU (memory-management unit); a USB 2.0 controller with an on-chip, 480-Mbps PHY (physical layer) with host and client support; a 32-bit PCI controller; and a 32-bit, 333-MHz DDR1/DDR2 (double-data-rate 1 and 2) memory controller. The integrated security engine provides hardware acceleration for the DES (Data Encryption Standard), 3DES (Triple DES), AES (Advanced Encryption Standard), SHA (Secure Hash Algorithm)-1, and MD (Message Digest)-5 algorithms.

The MPC8313E evaluation board sells for \$299. It includes a Linux 2.6 BSP (board-support package) with the CodeWarrior-based development tools that include a six-month evaluation license with no code-size restrictions. The Linux 2.6 BSP includes drivers for SATA, a four-port GigESwitch from Vitesse (www.vitesse.com), USB, IEEE 1588, and power management. The evaluation-board reference design uses the MPC8313E, which includes a CPE (customer-premises-equipment) formfactor board, schematic, and layout.

Initial samples of the MPC8313E are available now, general samples should debut in the first quarter of 2007, and general availability is scheduled for the second quarter. The 516-pin PBGA device uses Freescale's 90-nm-process technology, and it supports 1V core operation and 1.8, 2.5, 3.3V I/O operation.

-by Robert Cravotta

Freescale, www.freescale.com.

Micro/sys' latest ARM-based single-board computer delivers Power-over-Ethernet technology plus multiple onboard communication interfaces.

### **EPIC** computer expands communications options

argeting remote-terminal, data-logging, and protocol-conversion applications, Micro/sys recently introduced the SBC4670 single-board computer, which combines a low-power PX270 ARM (www.arm.com) processor with standard peripherals and multiple onboard communication formats. The SBC4670 provides optional support for serial protocols, including a socket modem for GSM/GPRS (Global System for Mobile communications/ General Packet Radio Service) or Bluetooth wireless, a serial-CAN (controller-area-network) bus, GPS (global positioning system), five serial ports, and 10/100BaseT Ethernet. For control and monitoring applications, the board features eight channels of 14-bit ADC, eight channels of 14bit DAC, and 24 channels of digital I/O. Available in a standard 4.5×6.5-in. EPIC (embedded-platform-for-industrial-computing) footprint, the SBC4670 also includes a watchdog timer, an SDRAM controller, a CompactFlash interface, and a USB-host controller. The board's 720-mA maximum-power draw allows you to power it remotely using POE (Power-over-Ethernet) technology.

The SBC4670 design includes a 16-bit PC/104 bus interface for access to many off-the-shelf boards, such as modems, analog I/O, or digital I/O. With 128 Mbytes of SDRAM and a 64-Mbyte resident flash array, the board supports the Linux, Windows CE, and VxWorks operating systems. Prices for the basic SBC4670 start at \$595 (one), and an industrial-temperature  $(-40 \text{ to } +85^{\circ}\text{C}) \text{ version is}$ also available for prices starting at \$650. Prices for development kits begin at \$950.

Micro/sys Inc. www. embeddedsys.com.

-by Warren Webb

#### **DILBERT By Scott Adams**

# Compact, Reliable, Embedded PCs

These go-anywhere SBCs operate where others can't. Rugged, reliable, and built for harsh environments, you will find PC-compatible architecture that will support Windows®, Linux, and x86-based software development tools.

- ▶ Platforms

- $PC/104 3.6 \times 3.8$  inches

- EPIC 4.5 x 6.5 inches

- EBX 5.75 x 8.00 inches

- ► Software Support

- Windows® XPe

- Linux 2.6

- Windows® CE

- x86-compatible RTOS

- Quick start development kits

- ▶ Input/Output

- A/D and D/A

- Digital

- Serial

- GPS

- USB 2.0

- ► Communication Expansion

- GSM/CDMA Cellular

- 802.11 a/b/g Wireless

- 10/100/1000 Mbps Ethernet

- ▶ Long-life product availability

- ▶ -40°C to +85°C operation

Our SBCs are the right choice for industrial, transportation, pipeline, instrumentation, and MIL/COTS applications.

Call 817-274-7553 or Visit www.winsystems.com Ask about our 30-day product evaluation!

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

### ESL market adds an enterprise player

adence Design Systems Inc is making an lenterprise-level play in the ESL (electronic-systemlevel)-software market by adding features to its Enterprise Manager environment, its Incisive Enterprise Simulator, and its new Palladium III emulator. Steve Glaser, corporate vice president of marketing in Cadence's verification division, says that most ESL-verification-tool flows now focus on the handoff between systems engineers (chip architects) and embedded-software developers. Glaser says, however, that ESL impacts several other disciplines in the flow and vice versa. These disciplines include hardware-design engineering, verification engineering, system-validation engineering and project management. Each of these disciplines interacts at some level, and the amount of interaction varies, depending on the nature of the design.

Glaser notes that the EDA industry hasn't yet produced a viable ESL-verification flow or even a tool to manage the scope of ESL within an enterprise. "The end goal of the customer is to get a predictable path to system quality and avoid re-spins. Even more important, errors at the system level can escape all the way to the end customer, ... and product recalls can be enormously expensive," he says. "We're helping groups take a closer look at the complexities of their designs and giving them a way to manage the risks of those complexities-from spec and planning all the way to closure."

To accomplish this task, Cadence has extended its Incisive Enterprise Manager envi-

ronment to form an ESL-flowmanagement system. Cadence last year released the Incisive Enterprise Manager. That product was a derivative of the vPlan and vManager products, which Verisity developed, and which Cadence acquired when it acquired Verisity in 2003. That version of Incisive Enterprise Manager allowed users to create an RTL (register-transferlevel)-to-gate-level verification plan to help design teams track verification progress and give them a better idea of whether they had done enough verification on a design. That version introduced management of assertion-based acceleration in PSL (Process Specification Language) and SVA (System Verilog Assertion) and transaction-based acceleration in SystemC and the e Testbench language. The version ran on the Incisive Enterprise Simulator and the Palladium II emulation system.

With this release, Cadence has extended the hardwareverification-plan and coveragemetric features of Incisive Enterprise Manager to embedded systems and software tools. Doing so allows enterprises to create ESL flows and track and analyze systemwide-verification activities, with the goal of refining the flow so that users can reduce time to market.

With this release, the company has also created an ESL option for its Incisive Enterprise Simulator. With the option, the simulator can now perform constrained random-scenario generation, and it includes a generic-software adapter that allows users to integrate embedded tools of their choice into the Cadence flow. The

We're giving them a way to manage the risks of those complexities—from spec and planning all the way to closure.

tool also supports the use of UVC (Universal Verification Component) verification IP (intellectual property). The UVCs send Incisive Enterprise Manager software subroutines in various sequences and measure coverage of those function calls. With the new ESL functions, users can also perform hardware-to-software debugging and failure analysis to test failures across the hardware-to-software boundary.

The company has also added algorithms to Incisive Enterprise Manager and the ESL option to the Incisive Enterprise Simulator to allow the new Palladium III emulator to run in the ESL environment. Ran Avinun, product-marketing-group director in the system-level-verification group, says the new Palladium III includes a 256 million-gate top capacity and double the runtime and debugging performance of the

Palladium II system. Emulation systems give users 100% visibility into the functions of their chip but typically run at speeds of only approximately 1 MHz. Furthermore, emulators are expensive. Avinun says that Palladium III will be attractive to traditional emulation users but that the new ties to ESL will potentially expand the usefulness of the emulation system to a broader number of users within an enterprise-groups looking at both hardware and software debugging.

Palladium III supports constrained random verification, as well as assertion-based acceleration in PSL and SVA and transaction-based acceleration in SystemC and the e Testbench language. Glaser claims that using Cadence's Enterprise ESL system will allow enterprises to cut time to market of IC projects by 50%. Prices for Enterprise Manager start at \$70,000 for subscription licenses, and prices for the Enterprise Simulator start at \$38,000. The ESL option costs \$11,000 for users who own the simulator. Cadence sells Palladium III systems, but for users lacking million-dollar budgets, the company offers leasing and remote access to the system for prices starting at \$150,000.

-by Michael Santarini Cadence Design Systems, www.cadence.com.

#### - FEEDBACK LOOP

"It is useful to turn the question 'what to do about energy supply?' on its head and ask 'what not to do?' And the answer to this question is clearly: 'Don't continue to grow populations.'"

—Tom Gosling in EDN's Feedback Loop at www.edn.com/ article/CA6399098. Add your comments.

# Design with confidence.

Introducing the new Stratix III family.

# Stratix III Family: The Lowest-Power High-Performance FPGAs

Building on the success of prior generations, Stratix® III FPGAs give you the highest performance available, while keeping power consumption to a minimum.

Design your next-generation systems with confidence.

Design with Stratix III FPGAs.

Supported by

The Programmable Solutions Company®

www.altera.com/confidence

Copyright © 2006 Altera Corporation, All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

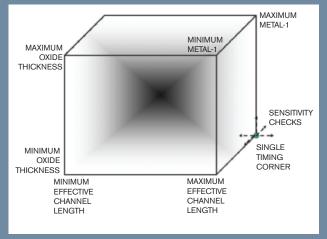

### Dummy-fill-synthesis tool has smarts

laze DFM is following up its mid-2006 release of its Blaze MO gate-CD biasing/leakage-control tool with an intelligent dummy-fill-"synthesis" tool. The tool addresses the problems that IC foundries encounter when they apply CMP (chemical mechanical polishing). Foundries apply CMP to each metal, via, and active polysilicon layer of a wafer to remove irregularities on the surface of each IC layer and to ensure that the layers have a smooth surface. But, in finer process geometries, CMP often errantly creates its own topographical variations-nonuniform layers, or "dishing"causing the features to work improperly. The CMP process can sometimes scrape away too much metal or distort features, causing electromigration or shorts. All these CMP-related problems adversely affect yield and product reliability. To counter CMP-dishing effects, engineers usually add dummy fill to even out layers.

Dave Reed, Blaze DFM's vice president of marketing, says that engineers have traditionally relied on DRC (design-rule-correction) scripts to determine the best places to insert dummy fill. Reed notes that, with every new process, the number of rules for CMP grows exponentially and the rules are typically too generalized, applying the same amount of fill if it fits a general situation. "Rules-based [fill] is what everybody has been using, but model-based is where everything is heading," says Reed. "We've been working closely with the foundries on their CMP models. The models are much easier to maintain and enhance than these rules-based scripts, and we're not even sure if people will be able to go even one more generation with these DRC scripts. Even today, they can't get an optimal result with just CMP scripts."

Working at 65-nm processes, companies are also now adding polysilicon fill to polysilicon layers to make the shapes look more regular for lithography tools, further complicating scripting. Andrew Kahng, PhD, the company's co-founder and chairman, and his team at the University of California—San Diego have found a way to formulate the fill problem so that solvers can solve it.

The Blaze IF tool reads CMP models from foundries and scripts from DRC tools. Third-party timing- and poweranalysis tools provide data to the tool, and it inserts dummy fill into design layouts to ensure density uniformity and thickness. "We think it will be used at the end of place and route," says Reed. "Anybody who knows timing, which will be the physical-design folks, should take responsibility for this now. Previously, this step took place during DRC. We don't think the physical-design guys should be responsible for your timing."

Users feed the tool SPEF (standard-parasitic-exchange-format), SDC (Synopsys-design-constraint), Verilog, and VCD (Verilog-changedump) files, along with a postplace-and-route database of LEF (library-exchange-format), DEF (data-exchange-format), GDSII (Graphic Design Sys-

tem II), and OA (Open Access) database files.

Cypress Semiconductor (www.cypress.com) was one of the tool's beta testers. On a project in 90-nm silicon, Cypress maintained ILD (interlayer-dielectric)-thickness variation that was 56% less than the company achieved with its own advanced-fill method.

Reed says that figure is especially impressive given that Cypress' fill method afforded the company only a 2% ILD improvement over using no fill at all. Blaze DFM licenses the Blaze IF for a \$250,000 annual subscription.

—by Michael Santarini ▶Blaze DFM Inc, www. blaze-dfm.com.

# WIQUEST ADDS VIDEO SUPPORT TO WIRELESS USB

For months now, rarely a week has passed when one Wireless USB player or another hasn't touted a chip compatible with the specifications that the WiMedia Alliance (www.wimedia.com) has shepherded. Based on UWB (ultrawideband) technology, broadly shipping Wireless USB products should hit the shelves in the first quarter of this year. After what seems like years waiting for the technology, you should expect a number of product announcements at the CES (Consumer Electronics Show, www.cesweb.org), which will take place Jan 8 to 11 in Las Vegas. Most of the recent buzz has been posturing about compliance with WiMedia standards. WiQuest, however, appears to be moving ahead with real products. The company has been on the forefront of FCC certification with its silicon. It recently received the alliance's certification for a Wireless USB-hub reference design. Although the end-product maker must ultimately earn certification, having the chip company go through the process with a reference design greatly eases the burden on the end-product manufacturer. Moreover, in mid-December, the company announced a video-enabled addition to its chip family.

The new chip set, WiDV (wireless digital video), enables in-room distribution of video, along with general Wireless USB capabilities. WiQuest's ICs support 1-Gbps data rates, which exceed the 480-Mbps rates that the Wireless USB standard specifies. Further, the company has added a proprietary video-compression capability to the latest WQUST100 chip set. Those features combine to enable transmission of HDTV-quality video over a range of 2 to 3m. The company foresees both PC and living-room applications for the new chip. For more on the chip set and a list of other players in the market, go to www.edn.com/article/CA6401216.—by Maury Wright

WiQuest, www.wiquest.com.

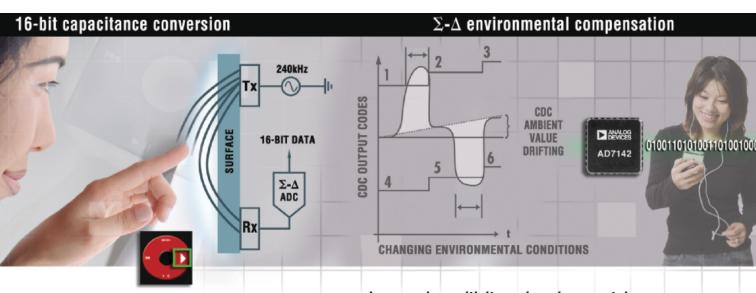

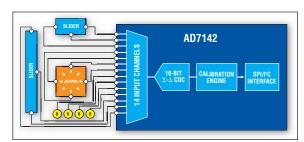

# 16-bit touch controller for the best user experience. In data conversion, analog is everywhere.

#### 16-bit $\Sigma$ - $\Delta$ CDC ...

- <1 femtofarad resolution</li>

- Full power mode: <1 mA

- Low power mode: 50 μA

- Shutdown current: <2 μA

- Supply voltage: 2.6 V to 3.6 V

- · Automatic environmental calibration

- · Automatic adaptive sensitivity

- SPI® or I2C® interface

- $\bullet$  32-lead 5 mm imes 5 mm LFCSP

- Price: \$1.65 (1k quantities)

#### ... enabling multiple applications

- Consumer electronics

- · Medical instrumentation

- · Automotive applications

- · Industrial equipment

- PC peripherals

With 14 inputs, the AD7142 can be programmed for a variety of navigation functions including buttons, sliders, scroll wheels, and joypads.

# Improved sensitivity and environmental calibration—made possible by $\Sigma\text{-}\Delta$ conversion

For products with increasing feature convergence, finger-driven navigation enhances the user experience—for designers as well as consumers. The AD7142 capacitance-to-digital converter (CDC) with on-chip environmental compensation delivers unmatched touch control performance. It offers:

- · Reliable performance over supply and temperature

- · Programmable functionality and touch sensitivity

- 50% lower power than competitive solutions

- Development tools, such as reference designs and host software, that reduce time to market

ADI also offers CDC solutions for measuring proximity, position, level, pressure, and humidity.

#### New online seminar:

View the "Innovative Human Interface Design Techniques Using CDCs" seminar at <a href="https://www.analog.com/onlineseminar-CDC">www.analog.com/onlineseminar-CDC</a>.

#### **A** GLOBAL DESIGNER

### Point-and-see picture transfer requires no setup, employs IrDA

s a long-term supplier of transceivers to the IrDA (Infrared Data Association) market, Sharp Microelectronics is promoting the IrSimple "special case" of that standard for sending pictures from camera phones to televisions. Sharp expects that this task—informal sharing of pictures among family or colleagues—will be an attractive feature for camera-

phone makers to offer. IrSimple allows fast picture transfer with virtually no setup procedure. Compared with the original IrDA specification—possibly one of the most widely deployed yet least-used interfaces—IrSimple increases transfer speed by stripping off most of the preamble and postdata "wrapping" that IrDA uses to ensure correct transmission and to facilitate re-

transmission of data blocks if any data is missing or corrupted. According to Sharp, the rationale is that, in the case of sending a picture for immediate display, users have equally immediate feedback if the transmission has failed; they see a poor picture or no picture at all. In that case, they can retransmit the picture themselves without the overhead of a protocol to do it for them.

The raw data rate remains the same as with IrDA 1.3: 4 Mbps. With the "reduced" protocol, the connection-setup time is 0.2 seconds as opposed to 3 seconds, and almost all the 4-Mbps data rate is available to deliver the payload, as opposed to an effective rate of

approximately 500 kbps with IrDA. The overall effect, Sharp says, is that a typical JPEG of 150 kbytes takes 0.5 seconds in IrSimple versus 5 seconds in IrDA. The company contends that the usage model-point the phone at the television from approximately 1m away and see the picture almost instantly-is an intuitive process that suits the task and may do the same for other informal, "closed-system" data transfers at lower cost than alternatives, such as Bluetooth or Wi-Fi. Bluetooth Version 1.1, Sharp points out, would take more than 30 seconds to transfer the same picture.

#### -by Graham Prophet, EDN Europe

**>Sharp**, www.sharpsme.com.

#### POWERING SOCs WITH INTEGRATED APPROACHES

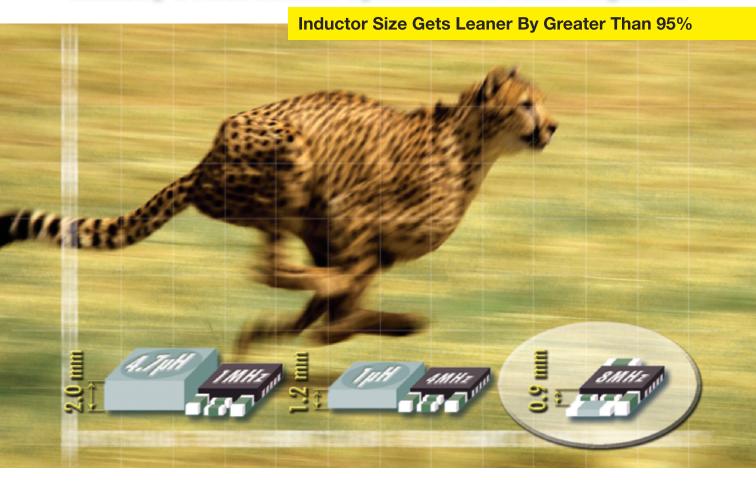

A typical portable electronic device, such as a mobile phone or an MP3 player, comprises a variety of chipsmany of which need different power-supply voltages. For instance, USB OTG (on the go) needs a 5V source, analog sections and interfaces require 3.3V, and RF chips need 2.5 and 1.8V sources. To compound the issue, current requirements for the chips vary, as does the quality of the power. Design engineers usually resort to a plethora of power-supply regulators with varying voltage, current, and noise specifications to meet the power demand, which results in a proliferation of power-regulator chips, consumption of precious board space, and increased bill-of-material costs. Spotting an opportunity, Cosmic Circuits has created a set of IP (intellectualproperty) cores that can integrate power regulators on an SOC (system on chip) to reduce component count and costs. The company has created about 10 types of power circuits in its Power-On SoC family on 130- and 90-nm TSMC (Taiwan Semiconductor Manufacturing Co, www. tsmc.com) process technology for various portable applications, including wireless LANs, MP3 players, UWB (ultrawideband) systems, and connectivity devices.

According to Krishnan Ramabadran, vice president of Cosmic Circuits, the principal challenge in designing the IP cores was to achieve high power efficiency in dc/dc-switching converters for battery-powered applications, even at low load currents. The space-constrained environment of portable electronic systems also means that Cosmic had

to design the cores in a way that would minimize the size of the inductors and capacitors on the board. The team also had to tackle 5V in a deep-submicron process to avoid the need for a step-down converter.

The company is now claiming a few industry firsts with its IP cores: a buck-boost converter that operates as low as 2.7V to extract the last bit of juice out of a battery; low-dropout regulators with a PSRR (power-supply-rejection-ratio) as high as 50 dB at 1 MHz; greater-than-90%-efficient capacitive switching regulators or charge pumps for supplying power to LEDs; a lithium-ion-battery charger that integrates a charging transistor in 130-nm digital-CMOS technology; and a super-low-power, low-dropout regulator that supplies trickle power to real-time-clock circuitry.

With many of the power blocks offering features and performance levels previously unavailable as IP to fabless companies, Cosmic is hopeful that it can become a supplier of choice to semiconductor-design houses in the consumer-electronics market. Ramabadran concedes that some applications may not benefit from this kind of power-management integration. For example, systems that require load currents exceeding 2A or those operating at input voltages of 9 to 12V could work equally well with designs based on discrete components rather than an SOC-integrated approach.—by Chitra Giridhar, EDN Asia

▶ Cosmic Circuits, www.cosmiccircuits.com.

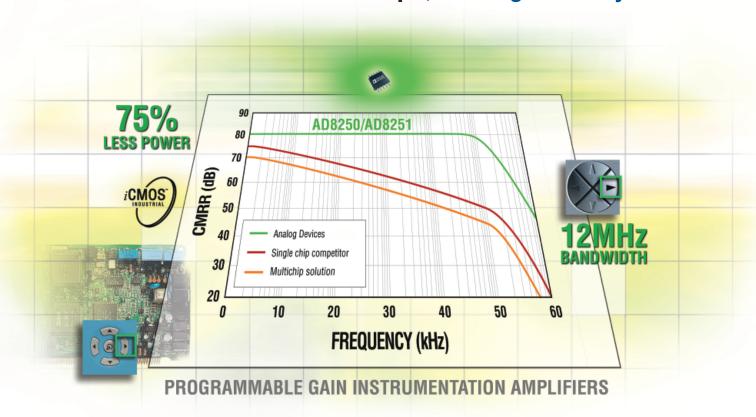

# Amplifiers Four Tondomon Pro ESSATE

# 80 dB CMRR @ 50 kHz, all in 15 mm<sup>2</sup>. With instrumentation amps, analog is everywhere.

# AD8250/AD8251: Programmable gain instrumentation amps (PGIA)

- Digital gain settings:

- G = 1, 2, 5, 10 (AD8250)

- $\bullet$  G = 1, 2, 4, 8 (AD8251)

- 3.5 mA supply current at 50 kHz, 75% lower than other offerings

- Slew rate: 20 V/μs

- $\bullet$  Settling time: 0.5  $\mu s$  to 0.01%

- · Gain drift: 10 ppm°C

- Input offset drift: 1  $\mu$ V/°C

- Input offset: 100 μV

- Price: \$4.95 @ 1k

#### For instrumentation applications

- Data acquisition

- · Biomedical analysis

- Test and measurement

- · Industrial process control

# Unmatched speed and accuracy at the lowest power consumption—just 3.5 mA

By delivering an unprecedented combination of 12 mHz bandwidth and outstanding dc precision, Analog Devices' AD8250/AD8251 programmable gain in-amps eliminate the need for compromise in instrumentation designs. With the industry's lowest power consumption and smallest footprint of any PGIA, these devices improve performance, allowing for greater channel densities.

The AD8250 and AD8251 leverage our innovative *i*CMOS™ (industrial CMOS) process technology to enable fast, accurate measurement

and robust signal conditioning over wide voltage ranges. These PGIAs are tailored to operate with high performance PulSAR® ADCs, such as the AD7621, AD7671, AD7685, and AD7946, as well as the ADR431 and ADR435 voltage references and ADG1209 multiplexer.

The AD8250/AD8251 are available in a 10-lead MSOP.

#### BY HOWARD JOHNSON, PhD

### Two-way street

uppose that I gave you a highway-traffic monitor that reports total traffic density on a section of roadway but does not provide separate figures for eastbound and westbound traffic. Obviously, this sensor reveals only part of the total traffic picture. Transmission lines, like streets, support traffic in two directions. A voltage probe connected to a transmission line acts much like a traffic-density sensor. It shows

an aggregate-voltage waveform but doesn't say which way the waveform is moving.

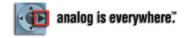

For example, **Figure 1** shows the composite voltage (pink) at capacitor  $C_3$  (**Reference 1**). The waveform shows a 200-psec step followed by a negative bump at B. To decipher the cause of that bump, include in your schematic a virtual (nonphysical)  $0\Omega$  resistor,  $R_0$ . Set all the parasitics associated with that component to their minimum values.

# Transmission lines, like streets, support traffic in two directions.

Export from your simulator both the voltage,  $v_0$ , at  $R_0$  and the current,  $i_0$ , flowing through  $R_0$ . Then, use the equations in **Figure 1** to compute both forward- and reverse-moving waveforms,  $v_E$  and  $v_B$ , respectively.

Figure 1 Voltage waveforms  $v_{\scriptscriptstyle E}$  and  $v_{\scriptscriptstyle D}$  propagate in opposite directions.

The composite waveform at  $C_3$  is the sum of these two waveforms. The forward waveform (blue) appears ideal. The negative bump appears only in the reverse waveform (purple). Therefore, the bump must be a reflection coming from something to the right of  $C_3$ .

Next, consider the shape and timing of the reflected bump. The bump duration is comparable with the signal rise time, so you may conjecture that it comes from one localized spot. The center of the bump occurs 400 psec after the midpoint of the initial rising edge. That 400-psec number is a round-trip reflection delay, so the imperfection you seek must be 200 psec downstream from R<sub>0</sub>. The only significant imperfection near that location is the receiver-load capacitance,  $C_4$ . If you remove C<sub>4</sub> from the circuit, the bump disappears, confirming C<sub>4</sub> as the source of the bump. A thorough examination of  $v_R$  reveals a second negative bump, smaller than the first, coincident with the main signal edge. That reflection comes from the  $C_3$ .

If this technique seems new or unusual to you, think back to when you were a little kid. Didn't your mother tell you to look both ways?

#### REFERENCE

Johnson, Howard, PhD, "Eye of the probe," *EDN*, Dec 1, 2006, pg 30, www.edn.com/article/CA6395495.

#### MORE AT EDN.COM

comment on this column.

🛨 Go to www.edn.com/070104hj and click on Feedback Loop to post a

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

founded by

PHILIPS

# ANIEL VASCONCELLOS

### Testing our reliance on testing

n the late 1980s, my company was in the market for its first CAE (computer-aided-engineering) system. Because we did a lot of mixed-signal design, we were particularly interested in being able to simulate those kinds of circuits. We developed a series of benchmark tests that included pure-digital circuits, pure-analog circuits, and one mixed-signal circuit. We based all of these circuits on real-life designs that we had recently worked with.

We were particularly careful when choosing the mixed-signal circuit. We wanted to have a realistic test but one that would also challenge the simulator. The circuit we chose, a microprocessor-controlled 4- to 20-mA converter, was ideal. We had thoroughly wrung out the design, through both analysis and testing, so we knew exactly how it worked. The circuit was in production and working flawlessly. We could control the simulations to drive the simulator to any circuit condition we wanted. We could con-

trol data to check response times and compare transient responses between the simulation and the real world. My team was ready for anything!

The first companies to get our testbench couldn't even begin to simulate the mixed-signal circuit. The output never got close to 20 mA. We gave each other smug looks and muttered: "Another case of marketing hype."

The last company to get the circuit was having trouble, too. The company's field-applications engineer called us up one day to talk about his problems.

"You say this is a working design?" ne asked.

"Yes," we replied. "It is in production and working perfectly."

"Well, my simulations can't get the circuit to drive up to 20 mA; it stops well below that." Again, my team members and I gave each other knowing looks. "But, when I changed the op-amp model from worst case to nominal, it started working." You could hear a pin drop in the room.

It turns out that the simulator's model assumed a worst-case supplyrail-to-output drop, resulting in less output swing than we needed. That worst-case drop prevented a pass transistor from fully turning on. Our vaunted circuit design was a dud! Despite exhaustive testing, we had never encountered an op amp with that much output drop. The analysis had missed it. It turns out that the designer felt that a worst-case analysis of the circuit was too difficult, so he ran "lots of tests." This situation was another example of why not to rely on testing to determine a design's limits: You will rarely encounter worst-case

Epilogue: We quietly implemented an engineering-change notice to change resistor values in the circuit so that it would work at worst-case conditions. We also bought that company's simulator and showed the designer how to run worst-case and Monte Carlo analyses.EDN

#### MORE AT EDN.COM

- + Visit EDN's Tales from the Cube Web page at www.edn.com/tales.

- To comment on this tale, click on Feedback Loop at www.edn.com/

070104tales.

Bob Mason is a senior engineer in the Engineered Solutions Center at Schneider Electric/Square D. Like Bob, you can share your Tales from the Cube and receive \$200. Contact Maury Wright at mgwright@edn. com.

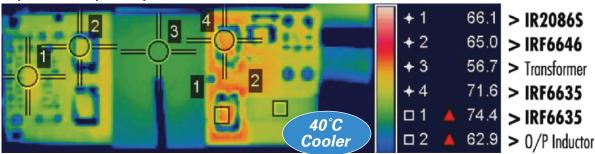

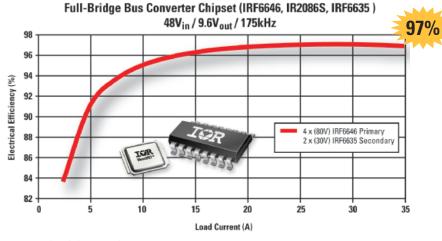

# **HOW COOL IS YOUR BRICK?**

IR's DC Bus Chipset Enables Converters with 48 $V_{IN}$ , 9.6 $V_{OUT}$ , 330W at 97% Efficiency and 40° Cooler

Chipset in this example is comprised of 3x IRF6646, 4x IRF6635, and 2x IR2086S

**New DC-DC Chipset Solution from International Rectifier**

| <b>DirectFET</b> ® | MOSFETs    |                    |                     |                                                                             |                        |                         |

|--------------------|------------|--------------------|---------------------|-----------------------------------------------------------------------------|------------------------|-------------------------|

| Part #             | Package    | V <sub>DSS</sub>   | R <sub>DS(on)</sub> | max @ V <sub>GS</sub> =10V                                                  | Q <sub>G</sub> Typical | Q <sub>GD</sub> Typical |

| IRF6644            | Medium can | 100V               | 13m $\Omega$        |                                                                             | 35nC                   | 11.5nC                  |

| IRF6655            | Small can  | 100V               |                     | $62\text{m}\Omega$                                                          | 8.7nC                  | 2.8nC                   |

| IRF6646            | Medium can | 80V                |                     | $9.5 \text{m}\Omega$                                                        | 36nC                   | 12nC                    |

| IRF6638            | Medium can | 30V                |                     | $2.9 m\Omega$                                                               | 30nC                   | 11nC                    |

| IRF6635            | Medium can | 30V                |                     | $1.8$ m $\Omega$                                                            | 47nC                   | 17nC                    |

| IRF6631            | Small can  | 30V                | $7.8$ m $\Omega$    |                                                                             | 12nC                   | 4.4nC                   |

| IRF6629            | Medium can | 25V                | $2.1$ m $\Omega$    |                                                                             | 34nC                   | 11nC                    |

| IRF6628            | Medium can | 25V                |                     | $2.5\text{m}\Omega$                                                         | 31nC                   | 12nC                    |

| IRF6622            | Small can  | 25V                | $6.3$ m $\Omega$    |                                                                             | 11nC                   | 3.8nC                   |

| Control IC         |            |                    |                     |                                                                             |                        |                         |

| Part #             | Package    | Voltage Rating   I |                     | Description                                                                 |                        |                         |

| IR2085S            | SO-8       | 100V               |                     | Primary-side half-bridge control IC, fixed 50% duty cycle, self-oscillating |                        |                         |

| IR2086S            | SO-16      | 100V               |                     | Primary-side full-bridge control IC, fixed 50% duty cycle, self-oscillating |                        |                         |

DirectFET® is a registered trademark of International Rectifier.

International Rectifier's new power management DC Bus converter chipset, featuring DirectFET® MOSFETs and proprietary ICs, delivers 48V<sub>in</sub>, 9.6V<sub>out</sub>, over 330W at 97% efficiency for networking and telecommunications systems ... at much cooler temperatures – up to 40°C!

- Achieves up to 1.5% better efficiency compared to industry standard quarter brick form factors

- Single DirectFET MOSFET can replace two S0-8 devices

- Reduces component count by > 45%

- Board space reduced by 29% vs. quarter brick form factors

- Industry best  $R_{DS(on)}$  for IRF6644 (13m $\Omega$ ), IRF6646 (9.5m $\Omega$ ), IRF6635 (1.8m $\Omega$ )

Design services and reference designs available at http://mypower.irf.com

THE POWER MANAGEMENT LEADER

+ Go to www.edn.com/070104prv to find additional illustrations and a list of manufacturers for more information.

# Under the hood of hybrid vehicles

Energy- and emission-efficient automobiles are increasingly relying on both combustion engines and electric motors for power.

he term "hybrid automobile" has held a number of meanings. An early use in the United States meant a vehicle of mixed national origins. Today, the term refers to vehicles that derive their propulsion from more than one type of power source. Hybrids are also vehicles that can use a mixture of multiple types of fuel, such as gasoline and ethanol-alcohol fuel. For this article, a hybrid vehicle is one that combines an internal combustion engine with electric batteries powering electric motors to provide force to the vehicle's wheels.

Parallel, serial, and power-split configurations are the most common configurations that hybrid vehicles use. The combustion engine provides most of the system energy. The graphic below shows a power-split configuration, but the types of subsystems and components are mostly similar among the different configurations. Three common hybrid modes are  $\mu$  hybrid, or assist; mild hybrid; and full hybrid. A  $\mu$ -hybrid mode uses the motor only to support improved starting and stopping of the vehicle rather than for fuel efficiency. A mild-hybrid mode adds recuperation

and acceleration boosting to the functions the motor supports. A full-hybrid mode further adds the ability for the power from the motor to supersede the combustion engine for

electric driving.

A parallel configuration provides higher efficiency, easier integration, and lower additional cost to the engine system. However, it couples the engine and motor speed. The Citroen C3 and the Honda Civic have used a parallel configuration in µ-, mild-, and full-hybrid modes.

A split-power configuration offers flexible configuration, which optimizes drive comfort and torque, but it is more complex because it requires two e-machines and a planetary gear. The Toyota Prius and the Lexus use the full-hybrid mode in a splitpower configuration.

A serial-hybrid configuration supports independent engine operation, but it suffers from lower efficiency and higher expense, because the system has two full-sized motors. The Orion uses this configuration in full-hybrid mode. EDN

The hybrid ECU (electrical-control unit) controls the electrical motor and the balance of the power delivered to the vehicle's transmission.

A battery is the primary source of energy to operate the electric motor. A high-voltage capacitor and an inverter condition the energy.

The electric motor operates under control of the hybrid ECU.

The internal combustion engine provides most of the energy the system uses for vehicle movement and battery recharging by burning fuel such as gasoline or diesel. The engine interfaces primarily to the generator.

Put the future of your design in the capable hands of Epson Toyocom, the worlds leading manufacturer of quartz timing devices.

\* By revenue, Epson Toyocom is the largest manufacturer of quartz devices in the world. (Data from Evalueserve Inc.)

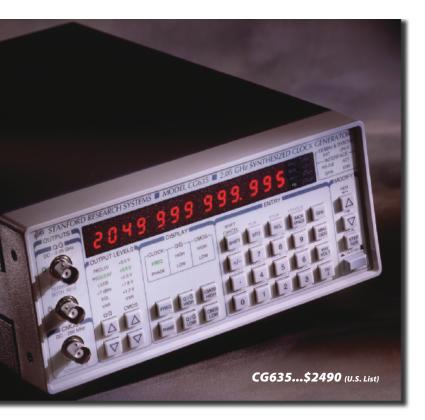

# You need this clock generator

CG635 - Precise, low jitter clocks from DC to 2.05 GHz

- · Square wave clocks from DC to 2.05 GHz

- Random jitter <1 ps (rms)</li>

- 80 ps rise and fall times

- · 16-digit frequency resolution

- · CMOS, LVDS, ECL, PECL, RS-485

- $\cdot$  Phase adjustment and time modulation

The CG635 Synthesized Clock Generator provides square wave clocks between DC and 2.05 GHz that are clean, fast and accurate. With jitter less than 1 ps, transition times of 80 ps, and 16 digits of frequency resolution, the CG635 will meet your most critical clock requirements.

The instrument can provide clocks at virtually any logic level via coax or twisted pairs. The outputs have less jitter than any pulse generator you can buy, with phase noise that rivals RF synthesizers costing ten times more.

Optional OCXO and rubidium timebases improve frequency stability by 100× and 10,000× over the standard crystal timebase. And an optional PRBS helps you evaluate high-speed serial data paths.

Whether you are trying to lower the noise floor of an ADC, increase SFDR of a fast DAC, or squash the bit error rate in a SerDes, the CG635 is the tool you need to get the job done.

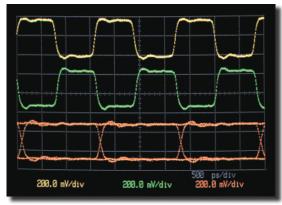

Clock and PRBS signals at 622.08 MHz

Plot shows complementary clock and PRBS (opt. 1) outputs at 622.08 Mb/s with LVDS levels. Traces have transition times of 80 ps and jitter less than 1 ps (rms).

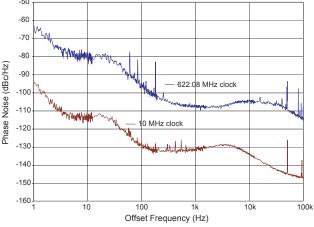

Phase noise for 10 MHz and 622.08 MHz outputs

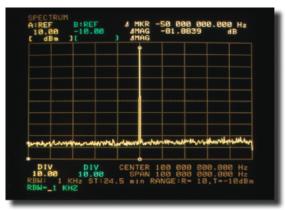

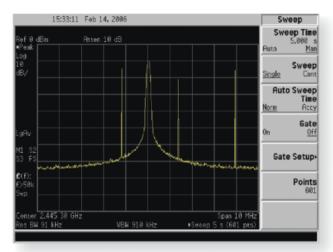

RF Spectrum of a 100 MHz clock

Graph shows a 100 MHz span around a 100 MHz clock. Only two features are present: the clock at 100 MHz, and the spectrum analyzer's noise floor (around -82 dBc).

Phone: (408)744-9040 www.thinkSRS.com

# ANALOG edge<sup>ss</sup>

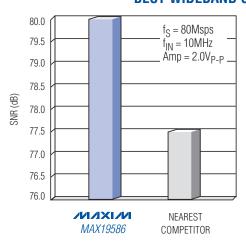

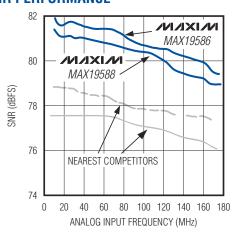

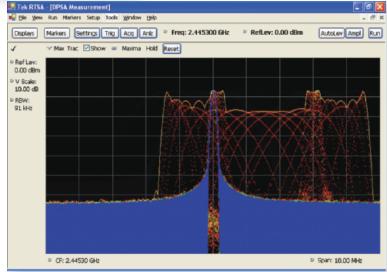

### Clocking High-Speed A/D Converters

**Application Note AN-1558**

James Catt, Applications Engineer

Extremely high-speed ADCs (>1 GSPS) demand a lowjitter sample clock in order to preserve Signal-to-Noise Ratio (SNR). These 8- and 10-bit converters have bestcase noise floors set by quantization noise. For an N-bit ADC sampling a full-scale sinusoid, the well known expression for SNR (in dB) is: SNR = 6.02N + 1.76. This sets the best case noise floor for an 8-bit ADC at -49.9 dBc. The noise floor degrades from this point due to factors such as jitter on the sample clock, intrinsic aperture jitter of the ADC, spurious components arising from non-linearities in the ADC quantizer, and other internal noise such as thermal noise. In this article, we look at the strategy for optimizing the performance of the sample clock based on PLL/VCO characteristics. This means minimizing overall integrated phase noise, which minimizes clock jitter.

The Root-Mean-Square (RMS) jitter of the sample clock combines with the intrinsic RMS aperture jitter of the ADC in a root-sum-square fashion to produce a total affective jitter. Total RMS jitter is:

$$\sigma_T = \sqrt{\sigma_{Clk}^2 + \sigma_{aperture}^2}$$

Equation 1

The SNR due to total jitter is:

$$SNR_{dB} = 20 \cdot \log \left( \frac{1}{2\pi f_{in} \sigma_{T}} \right) = 20 \cdot \log \left( \frac{1}{2\pi f_{in} \sqrt{\sigma_{Clk}^{2} + \sigma_{aperture}^{2}}} \right)$$

Solving for the maximum allowable clock jitter given some target SNR and ADC aperture jitter:

$$\sigma_{Clk} \leq \sqrt{\frac{1}{(2\pi f_{in})^2 \cdot 10^{\frac{SNR}{10}}} - \sigma_{aperture}^2} \quad Equation 3$$

The aperture jitter specification for National's ADC08D1500 8-bit, 1.5 GSPS converter is 400 femtoseconds (fs.). Using this value and a maximum input frequency of 748 MHz ( $f_{\rm IN}$ ), *Table 1* lists the allowable sample clock jitter for target SNR due to total jitter.

The third column of the table shows the combined SNR due to quantization noise and jitter for an 8-bit ADC, using a quantization noise SNR of 49.9 dB.

The allowable jitter (column 2) required to achieve a total SNR that is close to 49.9 dB is extremely difficult

| Target Jitter SNR<br>(dB) (Aperture<br>and Clock Jitter) | Allowable Clock<br>Jitter (fs) | Total SNR Due to Quantization Noise and Jitter (dB) $SNR = 10 \log \left(\frac{1}{\frac{1}{SNR_{c}} + \frac{1}{10^{10}}}\right)$ |

|----------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 54                                                       | 142                            | 48.5                                                                                                                             |

| 53                                                       | 259                            | 48.2                                                                                                                             |

| 52                                                       | 354                            | 47.8                                                                                                                             |

| 51                                                       | 447                            | 47.4                                                                                                                             |

| 50                                                       | 541                            | 46.9                                                                                                                             |

| 49                                                       | 640                            | 46.4                                                                                                                             |

| 48                                                       | 747                            | 45.8                                                                                                                             |

| 47                                                       | 862                            | 45.2                                                                                                                             |

| 46                                                       | 989                            | 44.5                                                                                                                             |

Table 1. Jitter SNR and Allowable Clock Jitter, with Total SNR

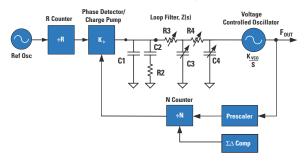

to achieve at a reasonable cost. However, achieving RMS clock jitter below 500 fs is possible using National's LMX2531LQ1500E frequency synthesizer combined with a high quality crystal reference oscillator. The LMX2531LQ1500E is shown in *Figure 1*.

Figure 1. LMX2531LQ1500E Simplified Block Diagram

For this example, we use the LMX2531LQ1500E to generate a fixed 1.5 GHz sample clock that can drive any of National's GSPS ADCs. Because the ADC clock is fixed, we can design the loop filter to achieve optimized phase noise performance, giving best jitter performance. Each functional block in *Figure 1* contributes some form of noise. The following table lists the low and high

frequency approximations for their noise transfer functions.

| Noise<br>Source         | Low Frequency<br>Transfer Function<br>Approximation | High Frequency<br>Transfer Function<br>Approximation |

|-------------------------|-----------------------------------------------------|------------------------------------------------------|

| Reference<br>Oscillator | N/R                                                 | G(s)                                                 |

| R Divider               | N                                                   | G(s)                                                 |

| N Divider               | N                                                   | G(s)                                                 |

| Phase<br>Detector       | N/Kφ                                                | G(s)                                                 |

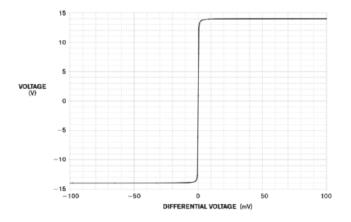

Table 2. Noise Transfer Functions, T(f)